電源設計人員的需求正變得越來越高,他們面臨著巨大的壓力,需要改善效率,降低成本,縮短產品開發周期。電源設計是一項復雜的工作,這一過程有許多校驗點。在電源設計系列專題中,我們將向您介紹10個設計階段中每個設計階段的測試要求,并給出小貼士,讓您的測試更高效,讓您的生活更輕松。

在這個階段中,我們將介紹在無負載、標稱負載和全負載條件下測試開關特點的各個步驟。

在開始前,應確保所有開關的啟動、關閉、占空比和死區時間都符合預期,如MOSFETs和IGBTs。泰克示波器包括一種高分辨率模式,從根本上提高了垂直分辨率,因此可以使用高精度計算啟動和關閉時間。

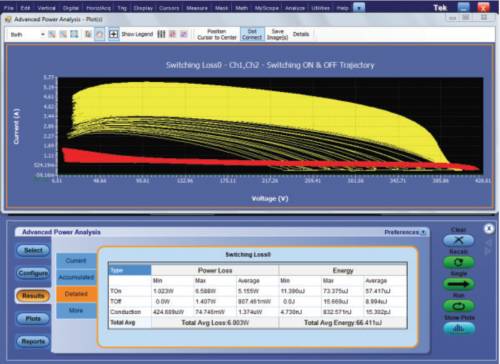

盡管電源的幾乎所有組件都會發生能量損耗,但絕大部分損耗發生在開關晶體管從關閉狀態轉換到打開狀態(或反之)的時候。使用所有開關周期的啟動損耗和關閉損耗的軌道圖(在DPOPWR軟件中提供),可以更加全面地了解開關損耗,如下圖所示。

開關/關閉軌道圖。

這時,要檢查所有 VGS 信號的噪聲和碰撞。這是一個重要步驟,因為這個端子上任何非預計的毛刺都可能會導致不想要的啟動和擊穿。為保證不可能出現擊穿,應檢查同步整流器或H橋接器的死區時間。

然后,檢驗門驅動器和相關儀器之間的定時關系,確保其與設計的計算結果相符。

為安全地測量非參考地電平的信號,我們建議使用相應額定電壓的差分探頭。一定不要浮動示波器,因為其會導致不好的結果。您可以考慮TDP1000、TDP0500或P6251高壓差分探頭,具體視應用而定。每種探頭都實現了高速寬帶采集和測量功能,提供了杰出的電氣性能、通用被測器件連接,而且都使用方便。

毫無疑問,很難測量浮動門信號。我們建議在門驅動器輸入上探測信號,這樣您可以檢驗頂部FET與底部FET之間的死區時間。

在低電壓轉換速率上測量電流也可以幫助您大限度地減少串擾,改善精度。