通常說(shuō)的信號(hào)完整性就是指信號(hào)無(wú)失真地進(jìn)行傳輸。前面我們討論很多信號(hào)完整性問題,包括時(shí)序、串?dāng)_、衰減、反射、電源完整性、EMC等等。

當(dāng)前的電子產(chǎn)品PCB上或多或少都有一些是高速信號(hào)網(wǎng)絡(luò)。在設(shè)計(jì)電路和PCB時(shí)就要多注意這些信號(hào)網(wǎng)絡(luò)的信號(hào)完整性。

對(duì)于很多工程師來(lái)講,信號(hào)完整性說(shuō)起來(lái)是一句很簡(jiǎn)單的話,但是很多時(shí)候卻要了硬件或者PCB設(shè)計(jì)工程師一條“老命”。本文主要針對(duì)PCB設(shè)計(jì)來(lái)討論,看看在PCB設(shè)計(jì)時(shí),有哪些點(diǎn)會(huì)導(dǎo)致信號(hào)完整性問題?

1、PCB材料選擇

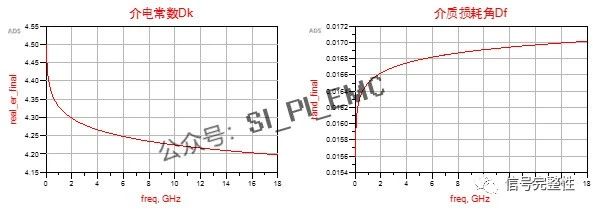

PCB使用什么樣的PCB材料會(huì)直接影響到信號(hào)完整性。比如PCB材料的介電常數(shù)、介質(zhì)損耗角、銅箔粗糙度、玻纖布等等參數(shù)都會(huì)影響信號(hào)的電氣性能。如下是PCB材料的介電常數(shù)和介質(zhì)損耗角隨著頻率變化的曲線。

PCB材料是基礎(chǔ),所以在設(shè)計(jì)PCB之前,要選擇好合適的PCB材料。

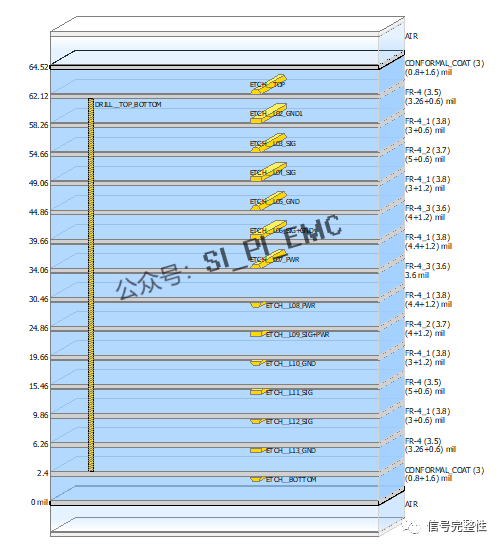

2、層疊設(shè)計(jì)

層疊設(shè)計(jì)是PCB設(shè)計(jì)中很重要的一步。如果層疊設(shè)計(jì)不合理,會(huì)直接導(dǎo)致設(shè)計(jì)存在天然的信號(hào)完整性問題。

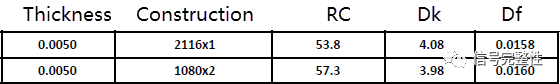

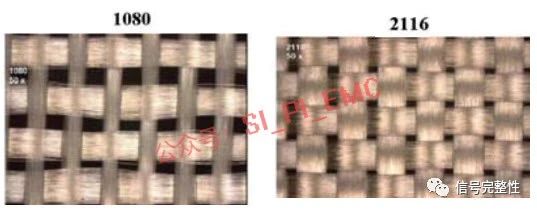

比如在設(shè)計(jì)層疊時(shí),我們通常都是按照厚度選擇,而對(duì)于相同的材料,也有很多種PP或者Core,那他們的性能并不是相同的,比如電氣參數(shù)Dk/Df、玻纖規(guī)格等。如下是某材料的兩種芯板:

雖然它們的厚度是一樣的,但它們分別是由1張2116的PP組成和2張1080的PP組成。其Dk和Df并不相同。這樣如果在設(shè)計(jì)層疊結(jié)構(gòu)的隨意使用,就會(huì)導(dǎo)致信號(hào)完整性的問題。同時(shí),1080和2116的玻纖也不一樣。

對(duì)于高速信號(hào),還要注意玻纖效應(yīng)的影響。關(guān)于玻纖效應(yīng),我們?cè)谇懊娴膬?nèi)容中也做過相關(guān)的介紹。

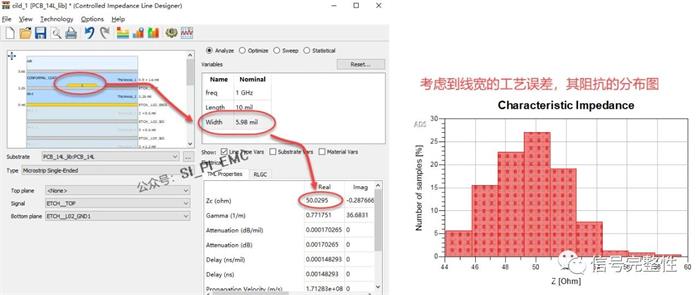

3、傳輸線的線寬

傳輸線的線寬是由阻抗決定的,根據(jù)總線或者芯片平臺(tái)的要求,確定好傳輸線的阻抗;再根據(jù)阻抗,在ADS CILD中計(jì)算傳輸線的線寬。

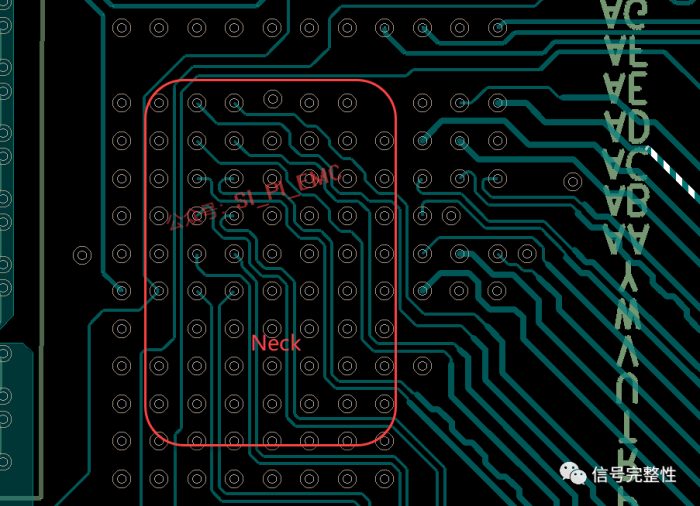

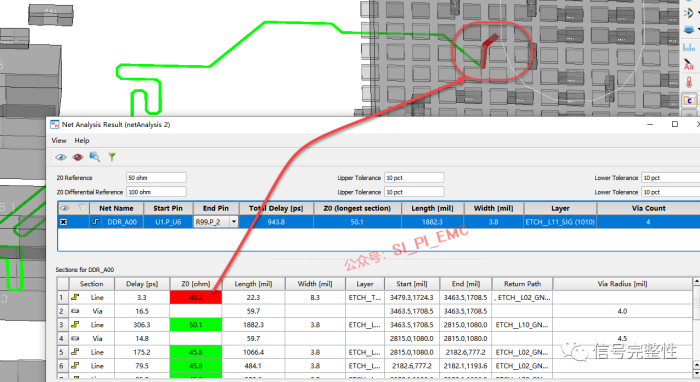

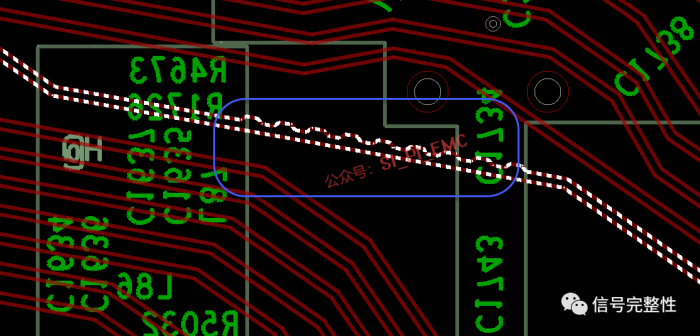

在設(shè)計(jì)PCB中,工程師都希望傳輸線的線寬是一致的,這樣設(shè)計(jì)效率是高的,但是這很難保證,因?yàn)楹芏嘈酒⑦B接器這類器件的pitch都可能會(huì)比較小,或者引腳的密度很高,就會(huì)導(dǎo)致在設(shè)計(jì)中會(huì)把線寬變小。如下圖所示:

線寬變化之后就會(huì)影響到信號(hào)完整性。在設(shè)計(jì)中要盡量減少這種線寬的變化,或者盡量縮短這種變化線寬的長(zhǎng)度,等等。

如果傳輸線太多,也可以考慮在ADS SIPro中使用RapidScan-Z快速掃描,查找到線寬變化,即阻抗不連續(xù)的點(diǎn)。

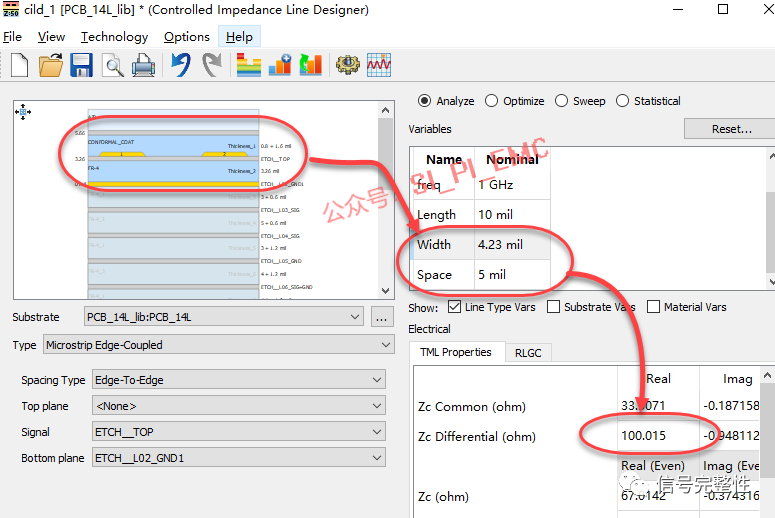

4、傳輸線之間的間距

在PCB設(shè)計(jì)中,傳輸線的間距有很多種類型,比如差分對(duì)內(nèi)的間距,不同類型的傳輸線之間的間距等等。不同的間距要求不同,如果是差分對(duì)之間的間距,則不能太近(小),也不能太遠(yuǎn)(大),由阻抗和設(shè)計(jì)要求決定。

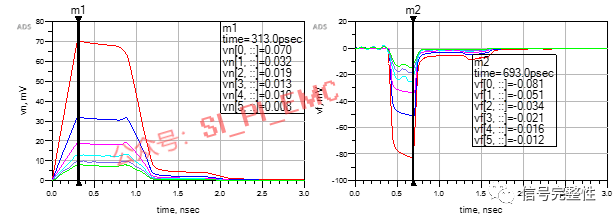

如果是不同類型傳輸線的間距,則希望間距盡量遠(yuǎn)一點(diǎn),這樣相互之間的串?dāng)_就會(huì)小,但是受限于空間和成本,這類間距也不能無(wú)限制的小。下面是隨著間距變化,串?dāng)_的變化趨勢(shì)。

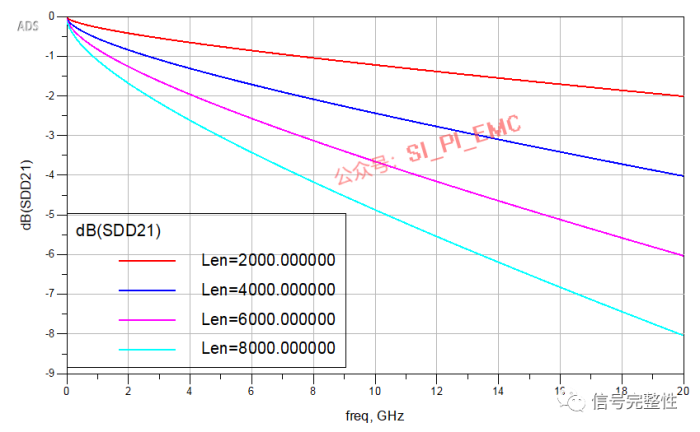

5、傳輸線的長(zhǎng)度

傳輸線的長(zhǎng)度由于產(chǎn)品結(jié)構(gòu)和實(shí)際設(shè)計(jì)決定。在沒有特殊要求的情況下,都希望傳輸線設(shè)計(jì)的短一點(diǎn)。因?yàn)閭鬏斁€越長(zhǎng),信號(hào)的衰減越大,能量損失越大。

如果傳輸線的長(zhǎng)度確實(shí)很長(zhǎng),而又不能縮短,這種情況下可以考慮換低損耗的板材或者在鏈路上使用repeater。

6、傳輸線等長(zhǎng)

等長(zhǎng)這個(gè)概念其實(shí)是工程師“偷(聰)懶(明)”想出來(lái)的。那我們還是沿用這個(gè)概念來(lái)談。傳輸線等長(zhǎng)包括差分對(duì)內(nèi)等長(zhǎng),也包括相同類型的傳輸線組內(nèi)等長(zhǎng)。如果傳輸線不等長(zhǎng)會(huì)帶來(lái)一些信號(hào)完整性的問題,包括時(shí)序不滿足要求、損耗過大或者容易受干擾等等。簡(jiǎn)單的方式就通過繞線使差分對(duì)不同的兩段傳輸線長(zhǎng)度一致。

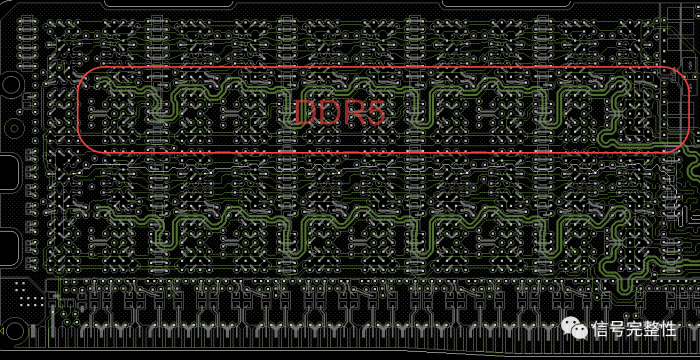

但是在之前的文章中也有給大家介紹過,實(shí)際上這種繞線等長(zhǎng),在電學(xué)當(dāng)中它并不能完全滿足設(shè)計(jì)要求。需要適當(dāng)?shù)卣{(diào)整,使傳輸線的延時(shí)是一致的才好。尤其是對(duì)于組內(nèi)等長(zhǎng)(DDR總線),要尤其注意等長(zhǎng)設(shè)計(jì)。

90%的工程師都沒意識(shí)到的高速電路設(shè)計(jì)問題:等長(zhǎng)繞線的影響

7、跨分割

在PCB設(shè)計(jì)中,工程師總會(huì)在不經(jīng)意間造成傳輸線跨分割。對(duì)于低速信號(hào)可能并不是什么問題,但是對(duì)于高速信號(hào)而言可能就會(huì)引起災(zāi)難性的結(jié)果。跨分割會(huì)引起阻抗不連續(xù)、反射、時(shí)序以及信號(hào)的輻射等等問題。

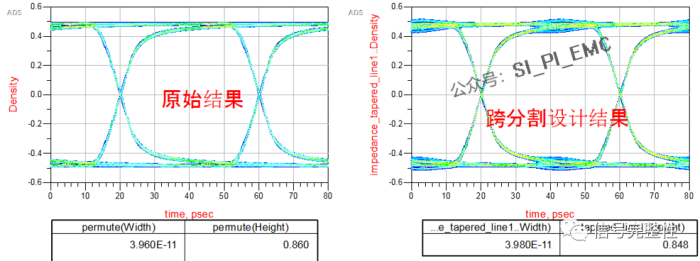

如下是對(duì)比跨分割設(shè)計(jì)與有完整參考平面設(shè)計(jì)的眼圖結(jié)果:

顯然,跨分割設(shè)計(jì)的結(jié)果會(huì)稍微差一些。在PCB設(shè)計(jì)中,如果不可避免跨分割設(shè)計(jì),信號(hào)完整性測(cè)試設(shè)備建議應(yīng)盡量減少跨分割傳輸線的長(zhǎng)度;尤其是當(dāng)信號(hào)速率比較高(比如25Gbps)時(shí),一旦出現(xiàn)跨分割就要謹(jǐn)慎評(píng)估,盡量避免跨分割。

8、拓?fù)浣Y(jié)構(gòu)

隨著電子技術(shù)的發(fā)展,越來(lái)越多的總線都采用點(diǎn)對(duì)點(diǎn)的設(shè)計(jì),但是有的總線也依然保留著多拓?fù)浣Y(jié)構(gòu)設(shè)計(jì),比如DDR總線,其時(shí)鐘、地址、控制、命令信號(hào)線。如下圖所示為DDR5時(shí)鐘信號(hào)的Flyby拓?fù)浣Y(jié)構(gòu):

Flyby拓?fù)浣Y(jié)構(gòu)設(shè)計(jì)就可能會(huì)造成阻抗的不連續(xù),如果要解決這類結(jié)構(gòu)造成的信號(hào)完整性問題,就需要做好傳輸線的阻抗補(bǔ)償、端接(或者調(diào)節(jié)ODT)等。

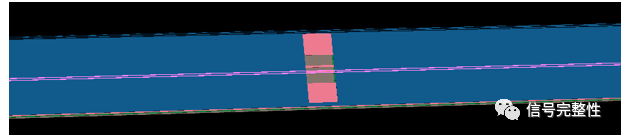

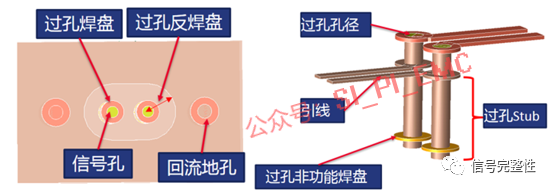

9、過孔

對(duì)于多層板的PCB設(shè)計(jì),過孔是不可或缺的。對(duì)于傳輸線而言,過孔往往會(huì)造成一些阻抗不連續(xù)、損耗變大等信號(hào)完整性問題。對(duì)于高速信號(hào)或者高頻信號(hào)的傳輸線過孔設(shè)計(jì),就需要優(yōu)化其過孔的結(jié)構(gòu),比如鉆孔的大小、焊盤、anti-pad、Via Stub等等。

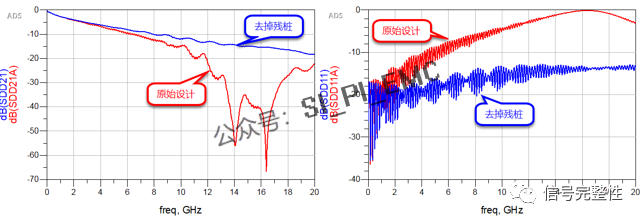

以下是在仿真軟件ADS中對(duì)比的Via Stub去掉與否的結(jié)果對(duì)比:

10、電源系統(tǒng)設(shè)計(jì)

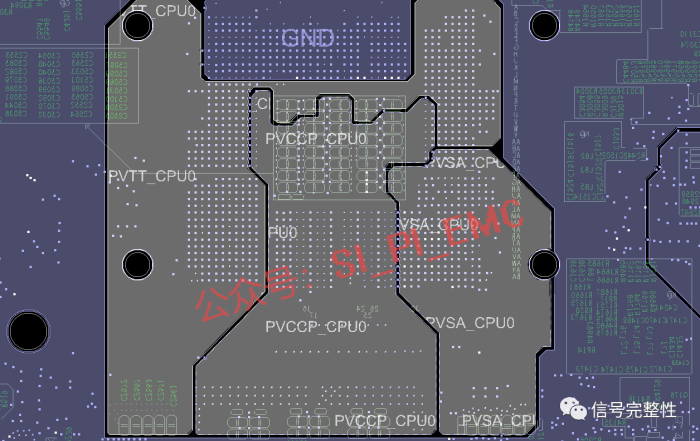

電源系統(tǒng)的設(shè)計(jì)是電子產(chǎn)品設(shè)計(jì)的重中之重,電源系統(tǒng)也是容易出問題的地方。在越來(lái)越復(fù)雜的電子系統(tǒng)中,一個(gè)電子系統(tǒng)中可能有10多組電源,或者有的更多,如下是之前設(shè)計(jì)過的一款服務(wù)器CPU處的部分電源平面設(shè)計(jì):

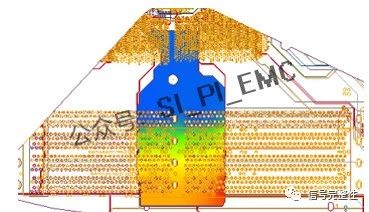

對(duì)于做系統(tǒng)產(chǎn)品的工程師而言,如何設(shè)計(jì)好電源主要分為兩個(gè)部分,一個(gè)是電源系統(tǒng)的電路設(shè)計(jì),一個(gè)是電源系統(tǒng)的PCB設(shè)計(jì)。在設(shè)計(jì)PCB時(shí)需要考慮到電源平面的分布和設(shè)計(jì)以及濾波電容的分布和擺放。為了更合理的設(shè)計(jì)好這些電源,盡量在設(shè)計(jì)之初和設(shè)計(jì)完成之后進(jìn)行電源完整性的仿真,盡早發(fā)現(xiàn)可能存在的問題。如下是一組電源的直流壓降仿真結(jié)果:

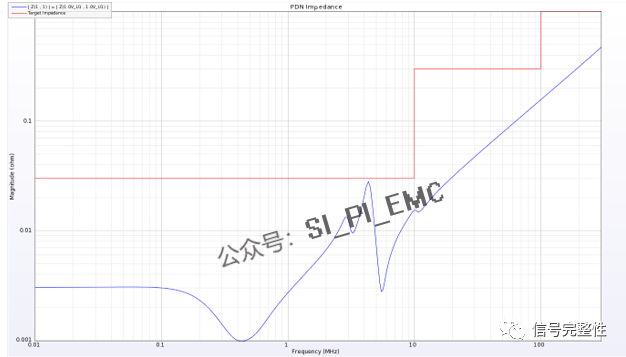

下圖是一組電源PDN阻抗分析結(jié)果:

11、總結(jié)

在越來(lái)越復(fù)雜、越來(lái)越高速、越來(lái)越緊湊的電子產(chǎn)品設(shè)計(jì)中,PCB設(shè)計(jì)的難度越來(lái)越高,信號(hào)完整性的問題也越來(lái)越多,問題也絕不僅限于本文所介紹的這些。不管任何設(shè)計(jì),在設(shè)計(jì)過程中要有好的設(shè)計(jì)習(xí)慣,設(shè)計(jì)前和設(shè)計(jì)后信號(hào)完整性測(cè)試設(shè)備建議盡量使用仿真工具進(jìn)行仿真分析。